# ADATA Technology Corp.

Half mSATA SSD Module Datasheet

IXM26-XXXGXX

# 1GB, 2GB, 4GB, 8GB, 16GB, 32GB, 64GB

Version 0

Document Number: R21-0245

ADATA Technology Co., Ltd. | www.adata-group.com T: +886-2-8228-0886 F: +886-2-8228-0887 2F, No. 258, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.) All rights are strictly reserved. Any portion of this paper shall not be reproduced, copied, or translated to any other forms without permission from ADATA Corporation.

# **Revision History**

| Revision No. | <u>History</u> | Draft Date    | <u>Remark</u> | Editor   |

|--------------|----------------|---------------|---------------|----------|

| 0            | Formal release | Jul. 16, 2013 |               | Andy Lin |

|              |                |               |               |          |

|              |                |               |               |          |

|              |                |               |               |          |

|              |                |               |               |          |

|              |                |               |               |          |

ADATA Technology Co., Ltd. | www.adata-group.com T: +886-2-8228-0886 F: +886-2-8228-0887

2F, No. 258, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

# **Table of Contents**

| 1.0 Product Description                                      |

|--------------------------------------------------------------|

| 1.1 Product Overview                                         |

| 1.2 Application Fields4                                      |

| 1.3 Features                                                 |

| 2.0 Mechanical Specification                                 |

| 2.1 PCBA Dimensions                                          |

| 2.2 Physical dimensions and Weight                           |

| 3.0 Electronic Specification                                 |

| 3.1 mSATA SSD Module Interface Connector and PIN Assignment7 |

| 3.2 SSD Function Block Diagram9                              |

| 3.3 ECC Description                                          |

| 4.0 Product Specifications                                   |

| 4.1 System Interface and Configuration11                     |

| 4.2 System Performance                                       |

| 4.3 Drive Capacity                                           |

| 4.4 Supply Voltage                                           |

| 4.5 System Power Consumption12                               |

| 4.6 System Reliability                                       |

| 4.7 Environmental Specifications12                           |

| 5.0 SATA Interface                                           |

| 5.1 Out of bank signaling14                                  |

| 5.2 COMRESET sequence state diagram15                        |

| 5.3 COMINIT                                                  |

| 5.4 Power on sequence timing diagram19                       |

| 5.5 ATA Command Register                                     |

| 5.6 ATA COMMAND SPECIFICATIONS                               |

| 6.0 Order Information                                        |

| 6.1 Model Number                                             |

| 6.2 Packing                                                  |

ADATA Technology Co., Ltd. | www.adata-group.com

T: +886-2-8228-0886 F: +886-2-8228-0887

2F, No. 258, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

# **1.0 Product Description**

# **1.1 Product Overview**

Taking the advantages of NAND flash memory, Solid State Drive (SSD) provides better solutions on durability, performance, and power efficiency over traditional hard disk drives. Employing dynamic/static wear-leveling technology to maximize device mean time between failures (MTBF), The SSD solutions are your best choice on wide-ranged mobile computing devices and consumer electronic products. With Half mSATA form factor (JEDEC MO-300B) or customized module form factor, The ADATA IXM26 Module SSD offers capacities from 1GB to 64GB using (SLC/MLC) NAND type flash memories.

# **1.2 Application Fields**

- Industrial PC and Thin Client

- Ticketing, Examining and Testing Machine

- Military, Health and Automatic Equipment

- Other machines and Equipment with mSATA interface slots on mother-board

# 1.3 Features

- Capacity: 4GB, 8GB, 16GB, 32GB (MLC)

- 1GB, 2GB, 4GB, 8GB, 16GB, 32GB (SLC)

- Compliance with JEDEC MO-300B Standard.

- Fully compatible with standard SATA I/II specifications

- Implement dynamic/static wear-leveling algorithm and ECC (Error Correction Code)

- Low power consumption

- No noise and no latency

- Shock resistance and anti-vibration

- Built-in Short Circuit Protection

- Built-in Thermal Shutdown Function

- Built-in Current Limit Function

- Fully compatible with OS that supports SATA standard (Windows XP, Vista, Window 7, Mac OS, and Linux)

- RoHS compliant

ADATA Technology Co., Ltd. | www.adata-group.com

T: +886-2-8228-0886 F: +886-2-8228-0887

<sup>2</sup>F, No. 258, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

All rights are strictly reserved. Any portion of this paper shall not be reproduced, copied, or translated to any other forms without permission from ADATA Corporation.

# 2.0 Mechanical Specification

# 2.1 PCBA Dimensions

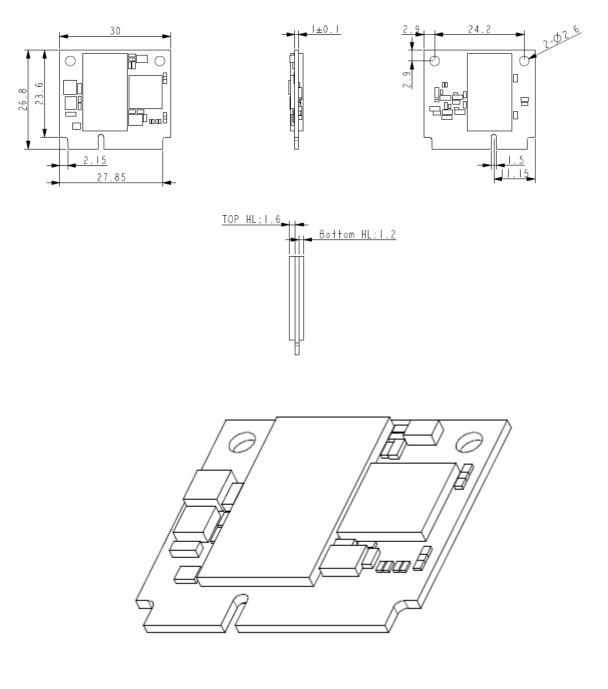

[Figure 2-1] PCBA Dimensions

ADATA Technology Co., Ltd. | www.adata-group.com

T: +886-2-8228-0886 F: +886-2-8228-0887

2F, No. 258, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

# 2.2 Physical dimensions and Weight

|            | Size      | 26.8 x 30 x 3.8mm (L x W x H) |

|------------|-----------|-------------------------------|

| Dimensions | Weight    | 4±1g                          |

|            | Connector | Standard mSATA golden finger  |

"All product specifications not covered in this document (electrical performance, appearance, etc.) are in accordance with ADATA's defined norms and standards. "

# **3.0 Electronic Specification**

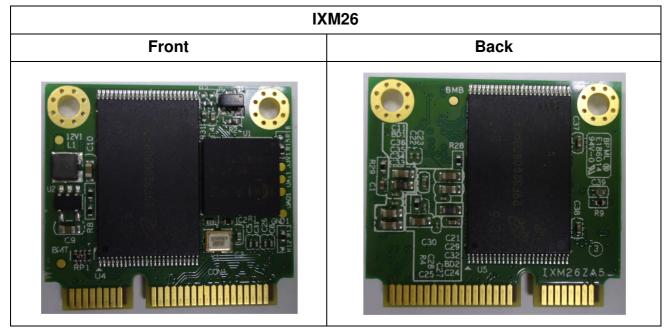

# 3.1 mSATA SSD Module Interface Connector and PIN Assignment

Device Connector: mSATA type 52 pin

| Pin# | Assignment | Description          | Pin# | Assignment | Description              |

|------|------------|----------------------|------|------------|--------------------------|

| 1    | N/A        | No Connect           | 27   | GND        | System ground            |

| 2    | +3.3V      | DC 3.3V input source | 28   | Reserved   | Reserved pin             |

| 3    | N/A        | No Connect           | 29   | GND        | System ground            |

| 4    | GND        | System ground        | 30   | N/A        | No Connect               |

| 5    | N/A        | No Connect           | 31   | SATA_RX-   | SATA Differential<br>RX- |

| 6    | Reserved   | Reserved pin         | 32   | N/A        | No Connect               |

| 7    | N/A        | No Connect           | 33   | SATA_RX+   | SATA Differential<br>RX+ |

| 8    | N/A        | No Connect           | 34   | GND        | System ground            |

| 9    | GND        | System ground        | 35   | GND        | System ground            |

| 10   | N/A        | No Connect           | 36   | Reserved   | Reserved pin             |

| 11   | N/A        | No Connect           | 37   | GND        | System ground            |

| 12   | N/A        | No Connect           | 38   | Reserved   | Reserved pin             |

| 13   | N/A        | No Connect           | 39   | +3.3V      | DC 3.3V input source     |

ADATA Technology Co., Ltd. | www.adata-group.com

T: +886-2-8228-0886 F: +886-2-8228-0887

2F, No. 25B, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

| Pin# | Assignment | Description              | Pin# | Assignment | Description          |

|------|------------|--------------------------|------|------------|----------------------|

| 14   | N/A        | No Connect               | 40   | GND        | System ground        |

| 15   | GND        | System ground            | 41   | +3.3V      | DC 3.3V input source |

| 16   | N/A        | No Connect               | 42   | N/A        | No Connect           |

| 17   | N/A        | No Connect               | 43   | N/A        | No Connect           |

| 18   | GND        | System ground            | 44   | N/A        | No Connect           |

| 19   | Reserved   | Reserved pin             | 45   | Reserved   | No Connect           |

| 20   | Reserved   | Reserved pin             | 46   | N/A        | No Connect           |

| 21   | GND        | System ground            | 47   | Reserved   | No Connect           |

| 22   | N/A        | No Connect               | 48   | Reserved   | Reserved pin         |

| 23   | SATA_TX+   | SATA Differential<br>TX+ | 49   | GND        | System ground        |

| 24   | +3.3V      | DC 3.3V input source     | 50   | GND        | System ground        |

| 25   | SATA_TX-   | SATA Differential<br>TX- | 51   | GND        | System ground        |

| 26   | GND        | System ground            | 52   | +3.3V      | DC 3.3V input source |

[Table 3-1] Pin Assignments

ADATA Technology Co., Ltd. | www.adata-group.com

T: +886-2-8228-0886 F: +886-2-8228-0887

2F, No. 258, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

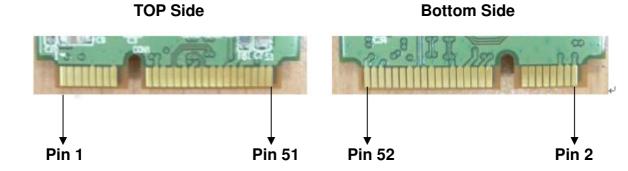

# 3.2 SSD Function Block Diagram

[Figure 3-2] Function Diagram

ADATA Technology Co., Ltd. | www.adata-group.com T: +886-2-8228-0886 F: +886-2-8228-0887 2F, No. 258, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

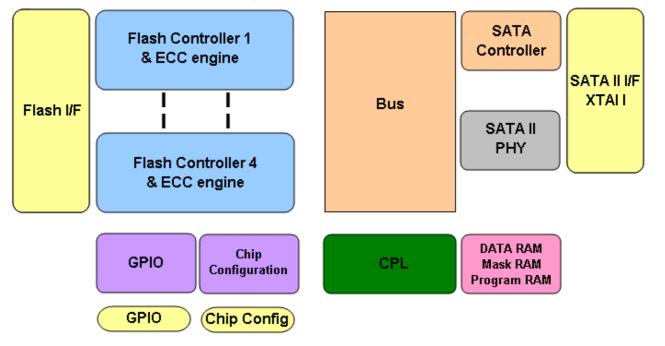

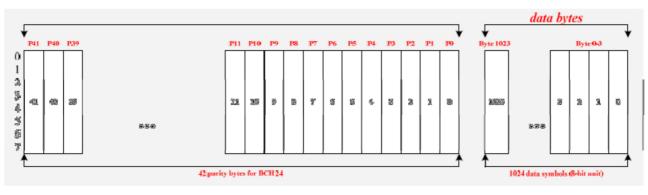

# 3.3 ECC Description

Please refer to FIG. 4 that is a diagram illustrating an allocating method of a spare area in each page of a NAND flash memory, where in the specific ECC algorithm utilizes a Bose, Chaudhuri and Hocquengham (BCH) ECC algorithm. When a BCH 16 ECC algorithm encodes the data in the NAND flash memory, the parity code generated in the encoding process may occupy 28 bytes of the spare area in each page. When a BCH 24 ECC algorithm encodes the data in the NAND flash memory, the parity code generated in the encoding process may occupy 42 bytes of the spare area in each page.

When a BCH 16 algorithm decodes the data in the NAND flash memory, the data can be decoded correctly if the error bit happened in two sector (1024Bytes) is 16. When a BCH 24 algorithm decodes the data in the NAND flash memory, the data can be decoded correctly if the error bit happened in two sector is 24.

[Figure 3-3] ECC Description

ADATA Technology Co., Ltd. | www.adata-group.com

T: +886-2-8228-0886 F: +886-2-8228-0887

2F, No. 258, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

## **4.0 Product Specifications**

# 4.1 System Interface and Configuration

- Burst read/write rate is 130 MB/sec (3.0 Gb/sec).

- Supports 1-port 1.5/3.0Gbps SATA I/II interface.

- Compliant with Serial ATA International Organization: Serial ATA Revision 2.6.

- Compliant SSD Allion compliance program.

## **4.2 System Performance**

The ADATA SSD meets the performance requirements listed in below table.

The performance was measured on a computer system with following setup:

- Platform: ASUA P5K3 Deluxe (Intel P35 + ICH9)

- Operation Systems: Windows XP SP3

- Testing Utility: CrystalDiskMark v3.0

|             | Windows OS                 |                             |  |

|-------------|----------------------------|-----------------------------|--|

| IXM26 (MLC) | Read (Minimum) / (Maximum) | Write (Minimum) / (Maximum) |  |

| 4GB         | 30MB/s / 34MB/s            | 5MB/s / 5.8MB/s             |  |

| .8GB        | 60MB/s / 66MB/s            | 10MB/s / 13MB/s             |  |

| 16GB        | 70MB/s / 75MB/s            | 15MB/s / 21MB/s             |  |

| 32GB        | 80MB/s / 84MB/s            | 35MB/s / 43MB/s             |  |

|             | Windows OS                 |                             |  |  |

|-------------|----------------------------|-----------------------------|--|--|

| IXM26 (SLC) | Read (Minimum) / (Maximum) | Write (Minimum) / (Maximum) |  |  |

| 1GB         | 60 MB/s / 70 MB/s          | 15MB/s / 22MB/s             |  |  |

| 2GB         | 70MB/s / 78MB/s            | 30MB/s / 36MB/s             |  |  |

| 4GB         | 70MB/s / 74MB/s            | 25MB/s / 30MB/s             |  |  |

| 8GB         | 75MB/s / 81MB/s            | 35MB/s / 42MB/s             |  |  |

| 16GB        | 80MB/s / 86MB/s            | 75MB/s / 81MB/s             |  |  |

| 32GB        | 80MB/s / 87MB/s            | 80MB/s / 85MB/s             |  |  |

Actual performance may vary depending on use conditions and environment

ADATA Technology Co., Ltd. | www.adata-group.com

T: +886-2-8228-0886 F: +886-2-8228-0887

2F, No. 25B, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

# 4.3 Drive Capacity

| Capacity | Cylinders | Heads | Sectors | Max LBA    |

|----------|-----------|-------|---------|------------|

| 1GB      | 1,959     | 16    | 63      | 1,974,672  |

| 2GB      | 3,897     | 16    | 63      | 3,928,176  |

| 4GB      | 7,773     | 16    | 63      | 7,835,184  |

| 8GB      | 16,383    | 16    | 63      | 15,649,200 |

| 16GB     | 16,383    | 16    | 63      | 31,277,232 |

| 32GB     | 16,383    | 16    | 63      | 62,533,296 |

# 4.4 Supply Voltage

| Item                   | Requirements      |

|------------------------|-------------------|

| Allowable voltage      | 3.3V ± 5%         |

| Allowable noise/ripple | 100mV p-p or less |

# 4.5 System Power Consumption

| Power              | Мах    |

|--------------------|--------|

| Active             | <2W    |

| Idle/Standby/Sleep | < 0.7W |

# 4.6 System Reliability

| MTBF | >1,000,000 Hours |

|------|------------------|

|------|------------------|

# **4.7 Environmental Specifications**

| Feature     | Commercial | industrial    |

|-------------|------------|---------------|

| Temperature | 0℃ to 70℃  | -40 ℃ to 85 ℃ |

ADATA Technology Co., Ltd. | www.adata-group.com

T: +886-2-8228-0886 F: +886-2-8228-0887

2F, No. 258, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

| Humidity  | $0^{\circ}$ C to 55 $^{\circ}$ C / 5%~95% RH, non-condensing |

|-----------|--------------------------------------------------------------|

| Vibration | 20G Peak, 80~2000Hz                                          |

| Shock     | 1500G, duration 0.5ms, Half Sine Wave                        |

\*Note: Depends on Flash memory specifications.

ADATA Technology Co., Ltd. | www.adata-group.com T: +886-2-8228-0886 F: +886-2-8228-0887

2F, No. 258, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

## 5.0 SATA Interface

### 5.1 Out of bank signaling

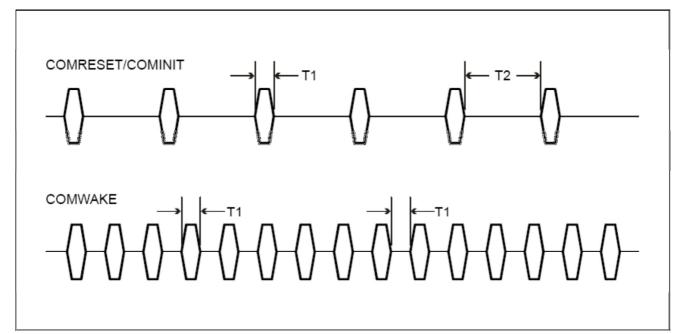

The shall be tree Out Of Band (OOB) signals used/ detected by the Phy: COMRESET, COMINIT, and COMWAKE. Each burst is followed by idle periods (at common-mode levels), having durations as depicted in following Figure and Table. The COMWAKE OOB signaling is used to bring the Phy out of a power-down state (Partial or Slumber).

There shall be three Out Of Band (OOB) signals used/detected by the Phy: COMRESET, COMINIT, and COMWAKE. COMINIT, COMRESET and COMWAKE OOB signaling shall be achieved by transmission of either a burst of four Gen1 ALIGNP primitives or a burst composed of four Gen1 Dwords with each Dword composed of four D24.3 characters, each burst having duration of 160 UIOOB. Each burst is followed by idle periods (at common-mode levels), having durations as depicted in Figure 6-1 and Table 6-1.

### [Figure 5-1] OOB signals

| Time Value                    |                              |  |  |  |

|-------------------------------|------------------------------|--|--|--|

| T1                            | 160 Uloob (106.7 ns nominal) |  |  |  |

| T2 480 Uloob (320 ns nominal) |                              |  |  |  |

| [Table 5-1] OOB Signal Times  |                              |  |  |  |

ADATA Technology Co., Ltd. | www.adata-group.com

T: +886-2-8228-0886 F: +886-2-8228-0887

2F, No. 258, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

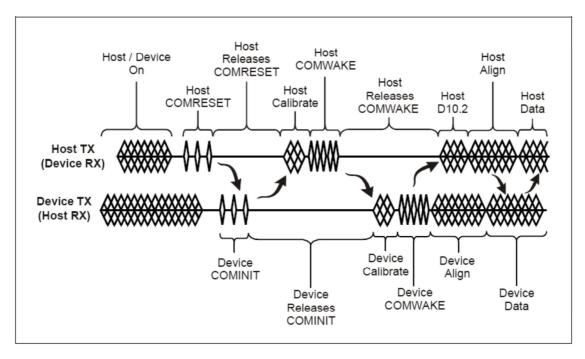

### 5.2 COMRESET sequence state diagram

COMRESET always originates from the host controller, and forces a hardware reset in the device. It is indicated by transmitting bursts of data separated by an idle bus condition. The OOB COMRESET signal shall consist of no less than six data bursts, including inter-burst temporal spacing. The COMRESET signal shall be:

1) Sustained/continued uninterrupted as long as the system hard reset is asserted, or 2) Started during the system hardware reset and ended some time after the negation of system hardware reset, or 3) Transmitted immediately following the negation of the system hardware reset signal.

The host controller shall ignore any signal received from the device from the assertion of the hardware reset signal until the COMRESET signal is transmitted. Each burst shall be 160 Gen1 UI's long (106.7 ns) and each inter-burst idle state shall be 480 Gen1 UI's long (320 ns). A COMRESET detector looks for four consecutive bursts with 320 ns spacing (nominal). Any spacing less than 175 ns or greater than 525 ns shall invalidate the COMRESET detector output. The COMRESET interface signal to the PHY layer shall initiate the Reset sequence shown in Figure 6-2 below. The interface shall be held inactive for at least 525 ns after the last burst to ensure far-end detector detects the negation properly.

## [Figure 5-2] COMRESET Sequence

ADATA Technology Co., Ltd. | www.adata-group.com

#### T: +886-2-8228-0886 F: +886-2-8228-0887

2F, No. 25B, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

### Description:

- 1. Host/device are powered and operating normally with some form of active communication.

- 2. Some condition in the host causes the host to issue COMRESET

- 3. Host releases COMRESET. Once the condition causing the COMRESET is released, the host releases the COMRESET signal and puts the bus in a quiescent condition.

- Device issues COMINIT When the device detects the release of COMRESET, it responds with a COMINIT. This is also the entry point if the device is late starting. The device may initiate communications at any time by issuing a COMINIT.

- 5. Host calibrates and issues a COMWAKE.

- 6. Device responds The device detects the COMWAKE sequence on its RX pair and calibrates its transmitter (optional). Following calibration the device sends a six burst COMWAKE sequence and then sends a continuous stream of the ALIGN sequence starting at the device's highest supported speed. After ALIGNP Dwords have been sent for 54.6us (2048 nominal Gen1 Dword times) without a response from the host as determined by detection of ALIGNP primitives received from the host, the device assumes that the host cannot communicate at that speed. If additional speeds are available the device tries the next lower supported speed by sending ALIGNP Dwords at that rate for 54.6 us (2048 nominal Gen1 Dword times.) This step is repeated for as many slower speeds as are supported. Once the lowest speed has been reached without response from the host, the device enters an error state.

- 7. Host locks after detecting the COMWAKE, the host starts transmitting D10.2 characters (see 7.6) at its lowest supported rate. Meanwhile, the host receiver locks to the ALIGN sequence and, when ready, returns the ALIGN sequence to the device at the same speed as received. A host shall be designed such that it acquires lock in 54.6us (2048 nominal Gen1 Dword times) at any given speed. The host should allow for at least 873.8 us (32768 nominal Gen1 Dword times) after detecting the release of COMWAKE to receive the first ALIGNP. This ensures interoperability with multi-generational and synchronous designs. If no ALIGNP is received within 873.8 us (32768 nominal Gen1 Dword times) the host restarts the power-on sequence repeating indefinitely until told to stop by the Application layer.

- 8. Device locks the device locks to the ALIGN sequence and, when ready, sends SYNCP indicating it is ready to start normal operation.

- 9. Upon receipt of three back-to-back non-ALIGNP primitives, the communication link is

ADATA Technology Co., Ltd. | www.adata-group.com

T: +886-2-8228-0886 F: +886-2-8228-0887

2F, No. 25B, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

established and normal operation may begin.

# **5.3 COMINIT**

COMINIT always originates from the drive and requests a communication initialization. It is electrically identical to the COMRESET signal except that it originates from the device and is sent to the host. It is used by the device to request a reset from the host in accordance to the sequence shown in Figure 6-3, below.

[Figure 5-3] COMINIT Sequence

Description:

- 1. Host/device are powered and operating normally with some form of active communication.

- 2. Some condition in the device causes the device to issues a COMINIT

- 3. Host calibrates and issues a COMWAKE.

- 4. Device responds The device detects the COMWAKE sequence on its RX pair and calibrates its transmitter (optional). Following calibration the device sends a six burst COMWAKE sequence and then sends a continuous stream of the ALIGN sequence starting at the device's highest supported speed. After ALIGNP Dwords have been sent

ADATA Technology Co., Ltd. | www.adata-group.com

T: +886-2-8228-0886 F: +886-2-8228-0887

2F, No. 25B, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

for 54.6 us (2048 nominal Gen1 Dword times) without a response from the host as determined by detection of ALIGNP primitives received from the host, the device assumes that the host cannot communicate at that speed. If additional speeds are available the device tries the next lower supported speed by sending ALIGNP Dwords at that rate for 54.6 us (2048 nominal Gen1 Dword times.) This step is repeated for as many slower speeds as are supported. Once the lowest speed has been reached without response from the host, the device enters an error state.

- 5. Host locks after detecting the COMWAKE, the host starts transmitting D10.2 characters (see section 7.6) at its lowest supported rate. Meanwhile, the host receiver locks to the ALIGN sequence and, when ready, returns the ALIGN sequence to the device at the same speed as received. A host shall be designed such that it acquires lock in 54.6 us (2048 nominal Gen1 Dword times) at any given speed. The host should allow for at least 873.8 us (32768 nominal Gen1 Dword times) after detecting the release of COMWAKE to receive the first ALIGNP. This ensures interoperability with multi-generational and synchronous designs. If no ALIGNP is received within 873.8 us (32768 nominal Gen1 Dword times) the host restarts the power-on sequence repeating indefinitely until told to stop by the Application layer.

- 6. Device locks the device locks to the ALIGN sequence and, when ready, sends SYNCP indicating it is ready to start normal operation.

- 7. Upon receipt of three back-to-back non-ALIGNP primitives, the communication link is established and normal operation may begin.

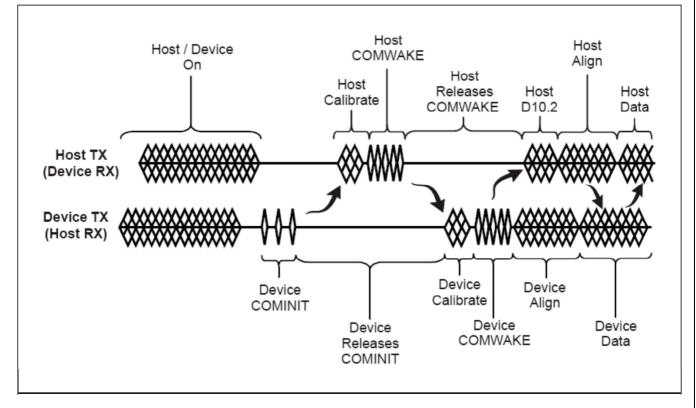

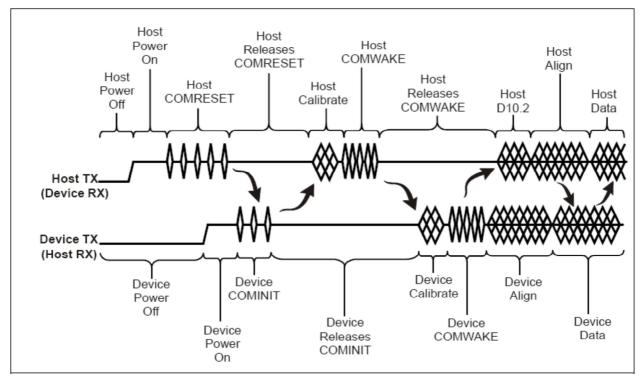

### 5.4 Power on sequence timing diagram

The following timing diagrams and descriptions are provided for clarity and are informative. The state diagrams provided in section 8.4 comprise the normative behavior specification and is the ultimate reference.

[Figure 5-4] Power on sequence

Description:

- 1. Host/device power-off Host and device power-off.

- 2. Power is applied Host side signal conditioning pulls TX and RX pairs to neutral state (common mode voltage).

- 3. Host issues COMRESET

- 4. Host releases COMRESET. Once the power-on reset is released, the host releases the COMRESET signal and puts the bus in a quiescent condition.

- 5. Device issues COMINIT When the device detects the release of COMRESET, it responds with a COMINIT. This is also the entry point if the device is late starting. The device may initiate communications at any time by issuing a COMINIT.

- 6. Host calibrates and issues a COMWAKE.

- 7. Device responds The device detects the COMWAKE sequence on its RX pair and

All rights are strictly reserved. Any portion of this paper shall not be reproduced, copied, or translated to any other forms without permission from ADATA Corporation.

calibrates its transmitter (optional). Following calibration the device sends a six burst COMWAKE sequence and then sends a continuous stream of the ALIGN sequence starting at the device's highest supported speed. After ALIGNP primitives have been sent for 54.6 us (2048 nominal Gen1 Dword times) without a response from the host as determined by detection of ALIGNP primitives received from the host, the device assumes that the host cannot communicate at that speed. If additional speeds are available the device tries the next lower supported speed by sending ALIGNP primitives at that rate for 54.6 us (2048 nominal Gen1 Dword times.) This step is repeated for as many slower speeds as are supported. Once the lowest speed has been reached without response from the host, the device shall enter an error state.

- 8. Host locks after detecting the COMWAKE, the host starts transmitting D10.2 characters (see 7.6) at its lowest supported rate. Meanwhile, the host receiver locks to the ALIGN sequence and, when ready, returns the ALIGN sequence to the device at the same speed as received. A host shall be designed such that it acquires lock in 54.6 us (2048 nominal Gen1 Dword times) at any given speed. The host should allow for at least 873.8 us (32768 nominal Gen1 Dword times) after detecting the release of COMWAKE to receive the first ALIGNP. This insures interoperability with multi-generational and synchronous designs. If no ALIGNP is received within 873.8 us (32768 nominal Gen1 Dword times) the host restarts the power-on sequence repeating indefinitely until told to stop by the Application layer.

- 9. Device locks the device locks to the ALIGN sequence and, when ready, sends the SYNCP primitive indicating it is ready to start normal operation.

- 10. Upon receipt of three back-to-back non-ALIGNP primitives, the communication link is established and normal operation may begin.

# 5.5 ATA Command Register

This table with the following paragraphs summarizes the ATA command set. Command Table

|                              |            | PARAMETERS USED |    |    |    |    |    |

|------------------------------|------------|-----------------|----|----|----|----|----|

| Command Name                 | Code       | SC              | SN | CY | DR | HD | FT |

| CHECK POWER MODE             | E5h        | 0               | Х  | Х  | 0  | Х  | Х  |

| DEVICE CONFIGURATION OVERLAY | B1h        | х               | х  | х  | 0  | х  | 0  |

| EXECUTE DIAGNOSTICS          | 90h        | Х               | Х  | Х  | 0  | Х  | Х  |

| FLUSH CACHE                  | E7h        | Х               | Х  | Х  | 0  | Х  | Х  |

| FLUSH CACHE EXT              | EAh        | Х               | Х  | Х  | 0  | Х  | Х  |

| IDENTIFY DEVICE              | ECh        | Х               | Х  | Х  | 0  | Х  | Х  |

| IDLE                         | E3h        | 0               | Х  | Х  | 0  | Х  | Х  |

| IDLE IMMEDIATE               | E1h        | Х               | Х  | Х  | 0  | Х  | Х  |

| NOP                          | 00h        | F               | F  | F  | 0  | Х  | 0  |

| INITIALIZE DEVICE PARAMETERS | 91h        | 0               | Х  | Х  | 0  | 0  | Х  |

| READ BUFFER                  | E4H        | Х               | Х  | Х  | 0  | Х  | Х  |

| READ DMA                     | C8h or C9h | 0               | 0  | 0  | 0  | 0  | Х  |

| READ DMA EXT                 | 25h        | 0               | 0  | 0  | 0  | 0  | Х  |

| READ FPDMA QUEUED            | 60h        | 0               | 0  | 0  | 0  | 0  | 0  |

| READ LOG EXT                 | 2Fh        | 0               | 0  | 0  | 0  | 0  | 0  |

| READ MULTIPLE                | C4h        | 0               | 0  | 0  | 0  | 0  | Х  |

| READ MULTIPLE EXT            | 29h        | 0               | 0  | 0  | 0  | 0  | Х  |

| READ NATIVE MAX ADDRESS      | F8h        | Х               | Х  | Х  | 0  | Х  | Х  |

| READ NATIVE MAX ADDRESS EXT  | 27h        | Х               | Х  | Х  | 0  | Х  | Х  |

| READ SECTOR(S)               | 20h or 21h | 0               | 0  | 0  | 0  | 0  | Х  |

| READ SECTOR(S) EXT           | 24h        | 0               | 0  | 0  | 0  | 0  | Х  |

| READ VERIFY SECTOR(S)        | 40h or 41h | 0               | 0  | 0  | 0  | 0  | Х  |

| READ VERIFY SECTOR(S) EXT    | 42h        | 0               | 0  | 0  | 0  | 0  | Х  |

| RECALIBRATE                  | 10h        | Х               | Х  | Х  | 0  | Х  | Х  |

| SECURITY DISABLE PASSWORD    | F6h        | Х               | Х  | Х  | 0  | Х  | Х  |

| SECURITY ERASE PREPARE       | F3h        | Х               | Х  | Х  | 0  | Х  | Х  |

| SECURITY ERASE UNIT          | F4h        | Х               | Х  | Х  | 0  | Х  | Х  |

ADATA Technology Co., Ltd. | www.adata-group.com

T: +886-2-8228-0886 F: +886-2-8228-0887

2F, No. 258, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

|                        | : •:=;     | _0, | , | •••• |   | , === | _, • |   |

|------------------------|------------|-----|---|------|---|-------|------|---|

| SECURITY FREEZE LOCK   | F5h        | Х   | Х | Х    | 0 | Х     | Х    |   |

| SECURITY SET PASSWORD  | F1h        | Х   | Х | Х    | 0 | Х     | Х    |   |

| SECURITY UNLOCK        | F2h        | Х   | Х | Х    | 0 | Х     | Х    |   |

| SEEK                   | 7xh        | Х   | Х | 0    | 0 | 0     | Х    |   |

| SET FEATURES           | EFh        | 0   | Х | Х    | 0 | Х     | 0    |   |

| SET MAX                | F9h        | 0   | 0 | 0    | 0 | 0     | 0    |   |

| SET MAX ADDRESS EXT    | 37h        | 0   | 0 | 0    | 0 | 0     | Х    |   |

| SET MULTIPLE MODE      | C6h        | 0   | Х | Х    | 0 | Х     | Х    |   |

| SLEEP                  | E6h        | Х   | Х | Х    | 0 | Х     | Х    |   |

| SMART                  | B0h        | Х   | Х | 0    | 0 | Х     | 0    |   |

| STANDBY                | E2h        | Х   | Х | Х    | 0 | Х     | Х    |   |

| STANDBY IMMEDIATE      | E0h        | Х   | Х | Х    | 0 | Х     | Х    |   |

| WRITE BUFFER           | E8h        | Х   | Х | Х    | 0 | Х     | Х    |   |

| WRITE DMA              | CAh or CBh | 0   | 0 | 0    | 0 | 0     | Х    |   |

| WRITE DMA EXT          | 35h        | 0   | 0 | 0    | 0 | 0     | Х    |   |

| WRITE DMA FUA EXT      | 3Dh        | 0   | 0 | 0    | 0 | 0     | Х    |   |

| WRITE FPDMA QUEUED     | 61h        | 0   | 0 | 0    | 0 | 0     | 0    |   |

| WRITE LOG EXT          | 3Fh        | 0   | 0 | 0    | 0 | 0     | Х    |   |

| WRITE MULTIPLE         | C5h        | 0   | 0 | 0    | 0 | 0     | Х    |   |

| WRITE MULTIPLE EXT     | 39h        | 0   | 0 | 0    | 0 | 0     | Х    |   |

| WRITE MULTIPLE FUA EXT | CEh        | 0   | 0 | 0    | 0 | 0     | Х    |   |

| WRITE SECTOR(S)        | 30h or 31h | 0   | 0 | 0    | 0 | 0     | Х    |   |

| WRITE SECTOR(S) EXT    | 34h        | 0   | 0 | 0    | 0 | 0     | Х    |   |

| WRITE VERIFY           | 3Ch        | 0   | 0 | 0    | 0 | 0     | 0    |   |

|                        |            |     |   |      |   |       |      | - |

Note:

- O = Valid, X = Don't care

- SC = Sector Count Register

- SN = Sector Number Register

- CY = Cylinder Low/High Register

- DR = DEVICE SELECT Bit (DEVICE/HEAD Register Bit 4)

- HD = HEAD SELECT Bit (DEVICE/HEAD Register Bit 3-0)

- FT = Features Register

T: +886-2-8228-0886 F: +886-2-8228-0887

2F, No. 258, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

ADATA Technology Co., Ltd. | www.adata-group.com

### **5.6 ATA COMMAND SPECIFICATIONS**

### CHECK POWER MODE (E5h)

The host can use this command to determine the current power management mode. Sector Count result value-

00h - device is in Standby mode

- 80h device is in Idle mode

- FFh device is in Active mode or Idle mode

### **DEVICE CONFIGURATION OVERLAY (B1h)**

Individual Device Configuration Overlay (DCO) feature set commands are identified by the value placed in the Feature field. The subcommands and their respective codes are listed below.

### **Device Configuration Overlay Feature field values**

| Value | Commands                         |

|-------|----------------------------------|

| C0h   | DEVICE CONFIGURATION RESTORE     |

| C1h   | DEVICE CONFIGURATION FREEZE LOCK |

| C2h   | DEVICE CONFIGURATION IDENTIFY    |

| C3h   | DEVICE CONFIGURATION SET         |

### DEVICE CONFIGURATION RESTORE (B1h/C0h)

The DEVICE CONFIGURATION RESTORE command provides a method for a host to restore any setting previously changed by a DEVICE CONFIGURATION SET command and to restore the content of the IDENTIFY DEVICE data, IDENTIFY PACKET DEVICE data, and other feature settings in a device to their factory default settings. The results of this action are indicated by the data returned from the Input Data of a DEVICE CONFIGURATION IDENTIFY command.

## DEVICE CONFIGURATION FREEZE LOCK (B1h/C1h)

The DEVICE CONFIGURATION FREEZE LOCK command provides a method for the host to prevent accidental modification of a device's DCO settings. After a device has completed a DEVICE CONFIGURATION FREEZE LOCK command without error, the device shall return command aborted for all DEVICE CONFIGURATION SET, DEVICE

2F, No. 258, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

CONFIGURATION FREEZE LOCK, DEVICE CONFIGURATION IDENTIFY, and DEVICE CONFIGURATION RESTORE commands until after the device processes a power-on reset. A device shall be in the factory\_config state or the reduced\_config state after processing a power-on reset. A device shall not exit the DCO\_Locked state as the result of processing a hardware reset or a software reset.

# DEVICE CONFIGURATION IDENTIFY (B1h/C2h)

The DEVICE CONFIGURATION IDENTIFY command causes a device to return a 512-byte data structure. The content of this data structure indicates the selectable commands, modes, and feature sets that the device is capable of disabling or modifying through processing of a DEVICE CONFIGURATION SET command. If a DEVICE CONFIGURATION SET command reducing a device's capabilities has completed without error, then:

- a) the response by a device to an IDENTIFY DEVICE, IDENTIFY PACKET DEVICE, and other commands, except the DEVICE CONFIGURATION IDENTIFY command, shall reflect the reduced set of capabilities; and

- b) the response by a device to a DEVICE CONFIGURATION IDENTIFY command shall reflect the entire set of selectable capabilities.

The phrase "is changeable" indicates that the feature may be disabled by the host using a DEVICE CONFIGURATION SET command. If the feature is not changeable then the device may support the feature but the DEVICE CONFIGURATION SET command shall not affect support of the feature.

The format of the Device Configuration Overlay data structure is listed below.

### DCO Identify data structure

| Word | Value  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0002h  | Data structure revision number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1    | 0007h  | Multiword DMA modes supported<br>Bit15:3 Reserved<br>Bit2 1 = Reporting support for Multiword DMA mode 2 and below is changeable<br>Bit1 1 = Reporting support for Multiword DMA mode 1 and below is changeable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      |        | Bit0 1 = Reporting support for Multiword DMA mode 0 is changeable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2    | 007Fh  | Ultra DMA modes supported<br>Bit15:7 Reserved<br>Bit6 1 = Reporting support for Ultra DMA mode 6 and below is changeable<br>Bit5 1 = Reporting support for Ultra DMA mode 5 and below is changeable<br>Bit4 1 = Reporting support for Ultra DMA mode 4 and below is changeable<br>Bit3 1 = Reporting support for Ultra DMA mode 3 and below is changeable<br>Bit2 1 = Reporting support for Ultra DMA mode 2 and below is changeable<br>Bit1 1 = Reporting support for Ultra DMA mode 1 and below is changeable<br>Bit0 1 = Reporting support for Ultra DMA mode 0 is changeable                                                                                                                                                                                                          |

|      | Native | Maximum LBA (QWord)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3-6  | MAX    | Bit63:48 Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | LBA    | Bit47:0 Maximum LBA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7    | 0089h  | Command set/feature set supported part 1<br>Bit15 Reserved<br>Bit14 1 = Reporting support for the Write-Read-Verify feature set is changeable<br>Bit13 1 = Reporting support for the SMART Conveyance self-test is<br>changeable<br>Bit12 1 = Reporting support for the SMART Selective self-test is changeable<br>Bit11 1 = Reporting support for the Forced Unit Access is changeable<br>Bit10 Reserved for TLC<br>Bit9 1 = Reporting support for the Streaming feature set is changeable<br>Bit8 1 = Reporting support for the 48-bit Addressing feature set is changeable<br>Bit7 1 = Reporting support for the HPA feature set is changeable<br>Bit6 1 = Reporting support for the AAM feature set is changeable<br>Bit5 1 = Reporting support for the TCQ feature set is changeable |

ADATA Technology Co., Ltd. | www.adata-group.com

T: +886-2-8228-0886 F: +886-2-8228-0887

2F, No. 258, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

|         |          | Bit4 1 = Reporting support for the PUIS feature set is changeable               |

|---------|----------|---------------------------------------------------------------------------------|

|         |          | bit 1 - Reporting support for the 1 of of feature set is changeable             |

|         |          | Bit3 1 = Reporting support for the Security feature set is changeable           |

|         |          | Bit2 1 = Reporting support for the SMART error log is changeable                |

|         |          | Bit1 1 = Reporting support for the SMART self-test is changeable                |

|         |          | Bit0 1 = Reporting support for the SMART feature set is changeable              |

|         |          | Serial ATA Command set/feature set supported                                    |

|         |          | Bit15:5 Reserved for Serial ATA                                                 |

|         |          | Bit4 1 = Reporting support for the SSP feature set is changeable                |

| 8       | 0000h    | Bit3 1 = Reporting support for asynchronous notification is changeable          |

|         |          | Bit2 1 = Reporting support for interface power management is changeable         |

|         |          | Bit1 1 = Reporting support for non-zero buffer offsets is changeable            |

|         |          | Bit0 1 = Reporting support for the NCQ feature set is changeable                |

| 9       | 0000h    | Reserved for Serial ATA                                                         |

| 10-20   | 0000h    | Reserved                                                                        |

|         |          | Command set/feature set supported part 2                                        |

|         |          | Bit15 1 = Reporting support for the NV Cache feature set is changeable          |

|         |          | Bit14 1 = Reporting support for the NV Cache Power Management feature set       |

|         |          | is changeable                                                                   |

| 01      | 00001    | Bit13 1 = Reporting support for WRITE UNCORRECTABLE EXT is                      |

| 21      | 0000h    | changeable                                                                      |

|         |          | Bit12 1 = Reporting support for the Trusted Computing feature set is            |

|         |          | changeable                                                                      |

|         |          | Bit11 1 = Reporting support for the Free-fall Control feature set is changeable |

|         |          | Bit10:0 Reserved                                                                |

| 00      | 00005    | Command set/feature set supported part 3                                        |

| 22      | 0000h    | Bit15:0 Reserved                                                                |

| 23-207  | 0000h    | Reserved                                                                        |

| 208-254 | 0000h    | Vender Specific                                                                 |

|         | Checksum | Integrity word                                                                  |

| 255     | +        | Bit15:8 Checksum                                                                |

| A5h     |          | Bit7:0 Signature                                                                |

#### ADATA Technology Co., Ltd. | www.adata-group.com

T: +885-2-8228-0886 F: +885-2-8228-0887

2F, No. 258, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

### DEVICE CONFIGURATION SET (B1h/C3h)

The DEVICE CONFIGURATION SET command allows a host to reduce the set of optional commands, modes, or feature sets supported by a device as indicated by a DEVICE CONFIGURATION IDENTIFY command. The DEVICE CONFIGURATION SET command may modify the data returned by IDENTIFY DEVICE or IDENTIFY PACKET DEVICE. When the IDENTIFY DEVICE data or IDENTIFY PACKET DEVICE data is changed, the device shall respond in a manner consistent with the new data.

If a bit is set to one in the DEVICE CONFIGURATION SET data transmitted to the device that is not set in the DCO data received from a DEVICE CONFIGURATION IDENTIFY command, no action is taken for that bit.

Modifying the maximum LBA of the device also modifies the LBA value returned by a READ NATIVE MAX ADDRESS or READ NATIVE MAX ADDRESS EXT command.

### **EXECUTE DIAGNOSITICS (90h)**

This command performs the internal diagnostic tests implemented by the drive. See ERROR register for diagnostic codes.

### FLUSH CACHE (E7h)

This command is used by the host to request the device to flush the write cache. If there is data in the write cache, that data shall be written to the media. The BSY bit shall remain set to one until all data has been successfully written or an error occurs.

### FLUSH CACHE EXT (EAh)

48-bit feature set mandatory command. This command is used by the host to request the device to flush the write cache. If there is data in the write cache, that data shall be written to the media. The BSY bit shall remain set to one until all data has been successfully written or an error occurs.

### **IDENTIFY DEVICE (ECh)**

This commands read out 512Bytes of drive parameter information. Parameter Information consists of the arrangement and value as shown in the following table. This command enables the host to receive the Identify Drive Information from the device.

ADATA Technology Co., Ltd. | www.adata-group.com

2F, No. 25B, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

T: +886-2-8228-0886 F: +886-2-8228-0887

### Identify Device Information Default Value

| Word  | Value | F/V | Description                                                   |  |  |  |  |

|-------|-------|-----|---------------------------------------------------------------|--|--|--|--|

|       |       |     | General configuration                                         |  |  |  |  |

|       |       | F   | 15 0 = ATA device                                             |  |  |  |  |

|       |       | х   | 14-8 Retired                                                  |  |  |  |  |

| 0     | 00405 | х   | 7-6 Obsolete                                                  |  |  |  |  |

| 0     | 0040h | х   | 5-3 Retired                                                   |  |  |  |  |

|       |       | V   | 2 Response incomplete                                         |  |  |  |  |

|       |       | х   | 1 Retired                                                     |  |  |  |  |

|       |       |     | 0 Reserved                                                    |  |  |  |  |

| 1     | 3FFFh | F   | Number of logical cylinders                                   |  |  |  |  |

| 2     | C837h | V   | Specific configuration                                        |  |  |  |  |

| 3     | 0010h | F   | Number of logical heads                                       |  |  |  |  |

| 4-5   | 0000h | Х   | Retired                                                       |  |  |  |  |

| 6     | 003Fh | F   | Number of logical sector per logical track                    |  |  |  |  |

| 7-8   | 0000h |     | Reserved for assignment by the CompactFlash_Association       |  |  |  |  |

| 9     | 0000h | Х   | Retired                                                       |  |  |  |  |

| 10-19 | XXXXh | F   | Serial number (20 ASCII characters)                           |  |  |  |  |

| 20-21 | 0000h | Х   | Retired                                                       |  |  |  |  |

| 22    | 0000h | Х   | Obsolete                                                      |  |  |  |  |

| 23-26 | XXXXh | F   | Firmware revision (8 ASCII characters)                        |  |  |  |  |

| 27-46 | XXXXh | F   | Model number (40 ASCII characters)                            |  |  |  |  |

|       |       | F   | 15-8 80h                                                      |  |  |  |  |

| 47    | 8001h | F   | 7-0 00h = Reserved                                            |  |  |  |  |

| 47    | F     | F   | 01h = Maximum number of 1 sectors on READ/WRITE MULTIPLE      |  |  |  |  |

|       |       |     | commands                                                      |  |  |  |  |

| 48    | 0000h | F   | Reserved                                                      |  |  |  |  |

|       |       |     | Capabilities                                                  |  |  |  |  |

|       |       |     | 15-14 Reserved for the IDENTIFY PACKET DEVICE command.        |  |  |  |  |

| 49    | 2F00h | F   | 13 1 = Standby timer values as specified in this standard are |  |  |  |  |

| τv    | 2,001 |     | supported                                                     |  |  |  |  |

|       |       |     | 0 = Standby timer values shall be managed by the device       |  |  |  |  |

|       |       | F   | 12 Reserved for the IDENTIFY PACKET DEVICE command.           |  |  |  |  |

ADATA Technology Co., Ltd. | www.adata-group.com

T: +886-2-8228-0886 F: +886-2-8228-0887

2F, No. 258, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

|           |        | _                                                                     | 11 1 = IORDY supported                                            |

|-----------|--------|-----------------------------------------------------------------------|-------------------------------------------------------------------|

|           |        | F                                                                     | 0 = IORDY may be supported                                        |

|           |        | F                                                                     | 10 1 = IORDY may be disabled                                      |

|           |        | F                                                                     | 9 1 = LBA supported                                               |

|           |        | Х                                                                     | 8 1 = DMA supported.                                              |

|           |        |                                                                       | 7-0 Retired                                                       |

|           |        |                                                                       | Capabilities                                                      |

|           |        | F                                                                     | 15 Shall be cleared to zero.                                      |

|           |        | F                                                                     | 14 Shall be set to one.                                           |

| 50        | 4000h  |                                                                       | 13-2 Reserved.                                                    |

|           |        | Х                                                                     | 1 Obsolete                                                        |

|           |        | F                                                                     | 0 Shall be set to one to indicate a device specific Standby timer |

|           |        |                                                                       | value minimum.                                                    |

| <b>F1</b> | 0000h  | F                                                                     | 15-8 PIO data transfer cycle timing mode                          |

| 51        | 0000h  |                                                                       | 7-0 Reserved                                                      |

| 52        | 0000h  | Х                                                                     | Obsolete                                                          |

|           |        | F                                                                     | 15-3 Reserved                                                     |

|           |        | F                                                                     | 2 1 = the fields reported in word 88 are valid                    |

|           |        |                                                                       | 0 = the fields reported in word 88 are not valid                  |

| 53        | 0007h  | F                                                                     | 1 1 = the fields reported in words 70:64 are valid                |

|           |        |                                                                       | 0 = the fields reported in words 70:64 are not valid              |

|           |        | х                                                                     | 0 1 = the fields reported in words 58:54 are valid                |

|           |        |                                                                       | 0 = the fields reported in words 58:54 are not valid              |

| 54        | XXXXh  | х                                                                     | Number of current cylinders                                       |

| 55        | 00XXh  | х                                                                     | Number of current heads                                           |

| 56        | XXXXh  | х                                                                     | Number of current sector per track                                |

| 57-58     | XXXXh  | Х                                                                     | Current capacity in sectors                                       |

|           |        |                                                                       | 15-9 Reserved                                                     |

|           |        | V                                                                     | 8 1 = Multiple sector setting is valid                            |

| 59 0101h  | V      | 7-0 xxh = Setting for number of sectors that shall be transferred per |                                                                   |

|           |        |                                                                       | interrupt on R/W Multiple command                                 |

| 60-61     | XXXXh  | F                                                                     | Total number of user addressable sectors                          |

| 62        | 0000h  | X                                                                     | Obsolete                                                          |

| 02        | 000011 |                                                                       |                                                                   |

ADATA Technology Co., Ltd. | www.adata-group.com

T: +885-2-8228-0886 F: +885-2-8228-0887

2F, No. 258, Lian Cheng Rd., Chung Ho Dist., New Taipei City 235, Taiwan (R.O.C.)

| 63     0007h     V     15-11     Reserved       63     0007h     V     8     1 = Multiword DMA mode 2 is selected       63     0007h     V     8     1 = Multiword DMA mode 1 is selected       63     0007h     V     8     1 = Multiword DMA mode 0 is selected       64     0     Multiword DMA mode 0 is not selected     7-3       73     Reserved     F     2     1 = Multiword DMA mode 1 and below are supported       76     0     1     1     Multiword DMA mode 0 is supported       76     0003h     F     2     1 = Multiword DMA mode 0 is supported       76     0003h     F     3     Reserved       76     0078h     F     Minimum Multiword DMA transfer cycle time per word       76     0078h     F     Minimum PIO transfer cycle time with IORDY flow control       77     0000h     Reserved     F     A-0       71-74     0000h     Reserved     F       71-74     0000h     Reserved for the IDENTIFY PACKET DEVICE command       71-74     0000h </th <th></th> <th></th> <th></th> <th></th>                                                      |          |        |                                    |                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|------------------------------------|--------------------------------------------------------------|

| 63   0007h   V   9   1 = Multiword DMA mode 2 is not selected     63   0007h   V   8   1 = Multiword DMA mode 1 is selected     63   0007h   V   8   1 = Multiword DMA mode 0 is selected     63   0007h   V   8   1 = Multiword DMA mode 0 is selected     63   0007h   V   8   1 = Multiword DMA mode 2 and below are supported     64   0   F   2   1 = Multiword DMA mode 1 and below are supported     64   0003h   F   1 = Multiword DMA mode 0 is supported     65   0078h   F   Minimum Multiword DMA transfer cycle time per word     66   0078h   F   Minimum PIO transfer cycle time without flow control     68   0078h   F   Minimum PIO transfer cycle time without flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     69-70   0000h   Reserved   Cueue depth     71-74   0000h   Reserved for the IDENTIFY PACKET DEVICE command     75   0000h   F5-5<                                                                               |          |        | F                                  | 15-11 Reserved                                               |

| 63   0007h   V   9   1 = Multiword DMA mode 1 is selected     63   0007h   V   8   1 = Multiword DMA mode 0 is selected     63   0007h   V   8   1 = Multiword DMA mode 0 is selected     64   0   = Multiword DMA mode 0 is not selected   7.3   Reserved     64   0003h   F   2   1 = Multiword DMA mode 0 is supported     65   0078h   F   7.0   Advanced PIO modes supported     66   0078h   F   Minimum Multiword DMA transfer cycle time per word     68   0078h   F   Minimum PIO transfer cycle time without flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     69-70   0000h   Reserved   Oueue depth     71-74   0000h   Reserved for the IDENTIFY PACKET DEVICE command     75   0000h   F   4-0     75   0000h   F   4-0     76   F   10   1 = Supports PHY Event Counts     7   9 <t< td=""><td></td><td></td><td>V</td><td>10 1 = Multiword DMA mode 2 is selected</td></t<>                                                         |          |        | V                                  | 10 1 = Multiword DMA mode 2 is selected                      |

| 63   0007h   V   8   1 = Multiword DMA mode 1 is not selected     63   0007h   V   8   1 = Multiword DMA mode 0 is selected     63   0007h   V   8   1 = Multiword DMA mode 0 is selected     64   7-3   Reserved     64   0003h   F   1   1 = Multiword DMA mode 0 is supported     65   0078h   F   Nanufacturer's recommended Multiword DMA transfer cycle time per word     66   0078h   F   Manufacturer's recommended Multiword DMA transfer cycle time     67   0078h   F   Minimum PIO transfer cycle time without flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     69-70   0000h   Reserved   Other the IDENTIFY PACKET DEVICE command     75   0000h   15-5   Reserved     71-74   0000h   Reserved for Serial ATA     75   0000h   15-5   Reserved     76 <td< td=""><td></td><td></td><td></td><td>0 = Multiword DMA mode 2 is not selected</td></td<>    |          |        |                                    | 0 = Multiword DMA mode 2 is not selected                     |

| 63   0007h   V   8   1 = Multiword DMA mode 0 is selected     7-3   Reserved     F   2   1 = Multiword DMA mode 2 and below are supported     F   1   1 = Multiword DMA mode 1 and below are supported     F   0   1 = Multiword DMA mode 0 is supported     64   0003h   F   0     7-0   Advanced PIO modes supported     65   0078h   F   Manufacturer's recommended Multiword DMA transfer cycle time per word     66   0078h   F   Manufacturer's recommended Multiword DMA transfer cycle time     67   0078h   F   Minimum PIO transfer cycle time without flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     69-70   0000h   Reserved   Cueue depth     71-74   0000h   Reserved for the IDENTIFY PACKET DEVICE command     75   0000h   15-5   Reserved     76   F   4-0   Maximum queue depth - 1     76   Serial ATA Capabilities   15-11   Reserved for Serial A                                                                          |          |        | V                                  | 9 1 = Multiword DMA mode 1 is selected                       |

| 0 = Multiword DMA mode 0 is not selected       7-3     Reserved       F     2     1 = Multiword DMA mode 2 and below are supported       F     1     1 = Multiword DMA mode 1 and below are supported       F     0     1 = Multiword DMA mode 0 is supported       64     0003h     F     7-0       7-0     Advanced PIO modes supported     65       65     0078h     F     Minimum Multiword DMA transfer cycle time per word       66     0078h     F     Manufacturer's recommended Multiword DMA transfer cycle time       67     0078h     F     Minimum PIO transfer cycle time without flow control       68     0078h     F     Minimum PIO transfer cycle time with IORDY flow control       68     0078h     F     Minimum PIO transfer cycle time with IORDY flow control       68     0078h     F     Minimum PIO transfer cycle time with IORDY flow control       68     0078h     F     Minimum PIO transfer cycle time with IORDY flow control       69-70     0000h     Reserved     F       71-74     0000h     Reserved for Serial ATA       75     000 |          |        |                                    | 0 = Multiword DMA mode 1 is not selected                     |

| 7-3   Reserved     F   2   1 = Multiword DMA mode 2 and below are supported     F   1   1 = Multiword DMA mode 1 and below are supported     64   0003h   F   7-0     65   0078h   F   Minimum Multiword DMA transfer cycle time per word     66   0078h   F   Minimum Multiword DMA transfer cycle time per word     66   0078h   F   Minimum PIO transfer cycle time without flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     69-70   0000h   Reserved   Reserved     71-74   0000h   Reserved for the IDENTIFY PACKET DEVICE command     75   0000h   15-5   Reserved     75   0000h   15-5   Reserved     76   F   10   1 = Supports PHY Event Counts     F   9   1 = Supports receipt of host initiated power management requests     8   1 = Supports the NCQ feature set   F                                                                                   | 63       | 0007h  | V                                  | 8 1 = Multiword DMA mode 0 is selected                       |

| F   2   1 = Multiword DMA mode 2 and below are supported     F   0   1 = Multiword DMA mode 1 and below are supported     64   0003h   F   0     F   7-0   Advanced PIO modes supported     65   0078h   F   Minimum Multiword DMA transfer cycle time per word     66   0078h   F   Manufacturer's recommended Multiword DMA transfer cycle time     67   0078h   F   Minimum PIO transfer cycle time without flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     69-70   0000h   Reserved   E     71-74   0000h   Reserved for the IDENTIFY PACKET DEVICE command     75   0000h   15-5   Reserved     76   F   4-0   Maximum queue depth – 1     76   0206h   F   10   1 = Supports PHY Event Counts                                                                                     |          |        |                                    | 0 = Multiword DMA mode 0 is not selected                     |

| F   1   1 = Multiword DMA mode 1 and below are supported     64   0003h   F   0   1 = Multiword DMA mode 0 is supported     64   0003h   F   7-0   Advanced PIO modes supported     65   0078h   F   Minimum Multiword DMA transfer cycle time per word     66   0078h   F   Manufacturer's recommended Multiword DMA transfer cycle time     67   0078h   F   Minimum PIO transfer cycle time without flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     69-70   0000h   Reserved      71-74   0000h   Reserved for the IDENTIFY PACKET DEVICE command     75   0000h   15-5   Reserved     75   0000h   15-5   Reserved     76   F   4-0   Maximum queue depth - 1     76   0206h   F   10   1 = Supports PHY Event Counts     76   9   1 = Supports the NCQ feature                                                                                                  |          |        |                                    | 7-3 Reserved                                                 |

| F     0     1 = Multiword DMA mode 0 is supported       64     0003h     F     15-8     Reserved       65     0078h     F     Minimum Multiword DMA transfer cycle time per word       66     0078h     F     Manufacturer's recommended Multiword DMA transfer cycle time       67     0078h     F     Minimum PIO transfer cycle time without flow control       68     0078h     F     Minimum PIO transfer cycle time with IORDY flow control       68     0078h     F     Minimum PIO transfer cycle time with IORDY flow control       69-70     0000h     Reserved       71-74     0000h     Reserved       75     0000h     F     4-0       75     0000h     F     4-0       75     0000h     F     4-0       76     6206h     F     10     1 = Supports PHY Event Counts       76     0206h     F     9     1 = Supports receipt of host initiated power management       76     7.3     Reserved for Serial ATA     8     1 = Supports SATA Gen2 Signaling Speed (3.0Gb/s)       71                                                                                |          |        | F                                  | 2 1 = Multiword DMA mode 2 and below are supported           |

| 64   0003h   F   15-8   Reserved     7-0   Advanced PIO modes supported     65   0078h   F   Minimum Multiword DMA transfer cycle time per word     66   0078h   F   Manufacturer's recommended Multiword DMA transfer cycle time     67   0078h   F   Minimum PIO transfer cycle time without flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     69-70   0000h   Reserved     71-74   0000h   Reserved     71-74   0000h   Reserved     75   0000h   F     64   0000h   Reserved     75   0000h   F     75   0000h   F     76   0206h   F                                                                                                                                                                                                                                                                                                                                |          |        | F                                  | 1 1 = Multiword DMA mode 1 and below are supported           |

| 64   0003h   F   7-0   Advanced PIO modes supported     65   0078h   F   Minimum Multiword DMA transfer cycle time per word     66   0078h   F   Manufacturer's recommended Multiword DMA transfer cycle time     67   0078h   F   Minimum PIO transfer cycle time without flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     69-70   0000h   Reserved   Reserved     71-74   0000h   Reserved for the IDENTIFY PACKET DEVICE command     75   0000h   15-5   Reserved     75   0000h   15-5   Reserved     75   0000h   15-11   Reserved for Serial ATA     76   0206h   F   10   1 = Supports PHY Event Counts     76   0206h   F   9   1 = Supports receipt of host initiated power management     76   0206h   F   7-3   Reserved for Serial ATA     70   1   1 = Supports the NCQ feature set   F     7   7-3   Reserved for Serial ATA   F     7   1   1 = Supports SATA Gen1 Signaling Speed (1.5                                                                                                                          |          |        | F                                  | 0 1 = Multiword DMA mode 0 is supported                      |

| F   7-0   Advanced PIO modes supported     65   0078h   F   Minimum Multiword DMA transfer cycle time per word     66   0078h   F   Manufacturer's recommended Multiword DMA transfer cycle time     67   0078h   F   Minimum PIO transfer cycle time without flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     69-70   0000h   Reserved     71-74   0000h   Reserved for the IDENTIFY PACKET DEVICE command     75   0000h   15-5   Reserved     75   0000h   15-5   Reserved     75   0000h   15-5   Reserved     76   F   4-0   Maximum queue depth – 1     Serial ATA Capabilities     15-11   Reserved for Serial ATA     F   10   1 = Supports PHY Event Counts     F   9   1 = Supports receipt of host initiated power management     F   7-3   Reserved for Serial ATA     F   2   1 = Supports SATA Gen2 Signaling Speed (3.0Gb/s) <td>64</td> <td>00026</td> <td></td> <td>15-8 Reserved</td>                                            | 64       | 00026  |                                    | 15-8 Reserved                                                |

| 66   0078h   F   Manufacturer's recommended Multiword DMA transfer cycle time     67   0078h   F   Minimum PIO transfer cycle time without flow control     68   0078h   F   Minimum PIO transfer cycle time with IORDY flow control     69-70   0000h   Reserved     71-74   0000h   Reserved     75   0000h   T5-5     75   0000h   15-5     76   F   4-0     76   0206h   F     76   0206h   F     76   0206h   F     76   1   1     76   0206h   F     7   3   Reserved for Serial A                                                                                                                                                                                                                                                                                                                                                                                       | 04       | 000311 | F                                  | 7-0 Advanced PIO modes supported                             |

| 67     0078h     F     Minimum PIO transfer cycle time without flow control       68     0078h     F     Minimum PIO transfer cycle time with IORDY flow control       69-70     0000h     Reserved       71-74     0000h     Reserved for the IDENTIFY PACKET DEVICE command       75     0000h     15-5     Reserved       75     0000h     15-5     Reserved       F     4-0     Maximum queue depth – 1       Serial ATA Capabilities     15-11     Reserved for Serial ATA       F     10     1 = Supports PHY Event Counts       F     9     1 = Supports receipt of host initiated power management       F     9     1 = Supports the NCQ feature set       7     7-3     Reserved for Serial ATA       F     2     1 = Supports SATA Gen2 Signaling Speed (3.0Gb/s)       F     1     1 = Supports SATA Gen1 Signaling Speed (1.5Gb/s)                                                                                                                                                                                                                              | 65       | 0078h  | F                                  | Minimum Multiword DMA transfer cycle time per word           |